Rift2Core

<a href="https://opensea.io/zh-CN/assets/ethereum/0x495f947276749ce646f68ac8c248420045cb7b5e/43473949287519253838889858564581990056411131273310467024990426327764908965888" target="_blank">

<img src='https://dl.openseauserdata.com/cache/originImage/files/d2f3860245aaa4b22de702b762cbea6c.png' align='right' alt='NFT' style='width:250px;height:250px'/>

</a>

Based on Chisel, Rift2Core is a 9-stage, N-issue(Configurable), out-of-order, 64-bits RISC-V Core, which supports RV64GC and M, S, U mode.

RiftCore is the previous version of Rift2Core in Verilog.

You can complete the deployment of the compilation and test environment following the steps below:

- Setup Repo

- ~~Setup sbt~~

- Setup mill

- Setup verilator and gtkwave

- ~~Compile chisel3 to verilog~~

- Compile chisel to verilog

- Compile Model of Rif2Chip

- Test a single ISA with waveform

- Test all ISA without waveform

Also we provide a Docker-Image mainly for CI, which can also be used for compiling and testing.

Rift To Go

Download Pre-compile Version Here, the newest status is as follows:

|Version|Test|Dhrystone|CoreMark|

|:----: |:--:|:-------:|:------:|

|Rift-2300|N/A|N/A|N/A|

|Rift-2310|N/A|N/A|N/A|

|Rift-2320|N/A|N/A|N/A|

|Rift-2330| |

| |

| |

|Rift-2340|N/A|N/A|N/A|

|Rift-2350|N/A|N/A|N/A|

|Rift-2360|N/A|N/A|N/A|

|Rift-2370|

|

|Rift-2340|N/A|N/A|N/A|

|Rift-2350|N/A|N/A|N/A|

|Rift-2360|N/A|N/A|N/A|

|Rift-2370| |

| |

| |

|Rift-2380|N/A|N/A|N/A|

|Rift-2390|N/A|N/A|N/A|

|

|Rift-2380|N/A|N/A|N/A|

|Rift-2390|N/A|N/A|N/A|

<!-- |Version|FIRRTL|Verilog|Test|Dhrystone|CoreMark|Area|

|:----: |:----:|:-----:|:--:|:-----:|:-----:|

|Rift-2300|[~Master~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2300/Rift2Chip.fir) [~Develop~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2300/Rift2Chip.fir)|[~Master~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2300/Rift2Chip.v) [~Develop~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2300/Rift2Chip.v)|N/A|N/A|N/A|

|Rift-2310|[~Master~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2310/Rift2Chip.fir) [~Develop~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2310/Rift2Chip.fir)|[~Master~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2310/Rift2Chip.v) [~Develop~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2310/Rift2Chip.v) |N/A|N/A|N/A|

|Rift-2320|[~Master~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2320/Rift2Chip.fir) [~Develop~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2320/Rift2Chip.fir)|[~Master~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2320/Rift2Chip.v) [~Develop~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2320/Rift2Chip.v) |N/A|N/A|N/A|

|Rift-2330|[Master](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2330/Rift2Chip.fir) [Develop](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2330/Rift2Chip.fir)|[Master](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2330/Rift2Chip.v) [Develop](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2330/Rift2Chip.v) |Pass|N/A|N/A|

|Rift-2340|[Master](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2340/Rift2Chip.fir) [Develop](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2340/Rift2Chip.fir)|[Master](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2340/Rift2Chip.v) [Develop](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2340/Rift2Chip.v) |N/A|N/A|N/A|

|Rift-2350|[Master](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2350/Rift2Chip.fir) [Develop](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2350/Rift2Chip.fir)|[Master](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2350/Rift2Chip.v) [Develop](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2350/Rift2Chip.v) |N/A|N/A|N/A|

|Rift-2360|[Master](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2360/Rift2Chip.fir) [Develop](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2360/Rift2Chip.fir)|[Master](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2360/Rift2Chip.v) [Develop](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2360/Rift2Chip.v) |N/A|N/A|N/A|

|Rift-2370|[Master](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2370/Rift2Chip.fir) [Develop](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2370/Rift2Chip.fir)|[Master](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2370/Rift2Chip.v) [Develop](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2370/Rift2Chip.v) |Pass|1.281689|1.912046|

|Rift-2380|[~Master~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2380/Rift2Chip.fir) [~Develop~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2380/Rift2Chip.fir)|[~Master~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2380/Rift2Chip.v) [~Develop~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2380/Rift2Chip.v) |N/A|N/A|N/A|

|Rift-2390|[~Master~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2390/Rift2Chip.fir) [~Develop~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2390/Rift2Chip.fir)|[~Master~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/master/Release/Rift2390/Rift2Chip.v) [~Develop~](https://raw.githubusercontent.com/whutddk/Rift2Core/gh_pages/Verilog/develop/Release/Rift2390/Rift2Chip.v) |N/A|N/A|N/A| -->

API

Rift2Core is not only an extremely configurable RISC-V CPU generator, but also provides configurable generation of submodules.

Search the provided API in the Scala Doc.

API Here

Wiki

Wiki in Chinese

Wiki in English(Comming Soon!)

Sponsorships

Micro-Architecture

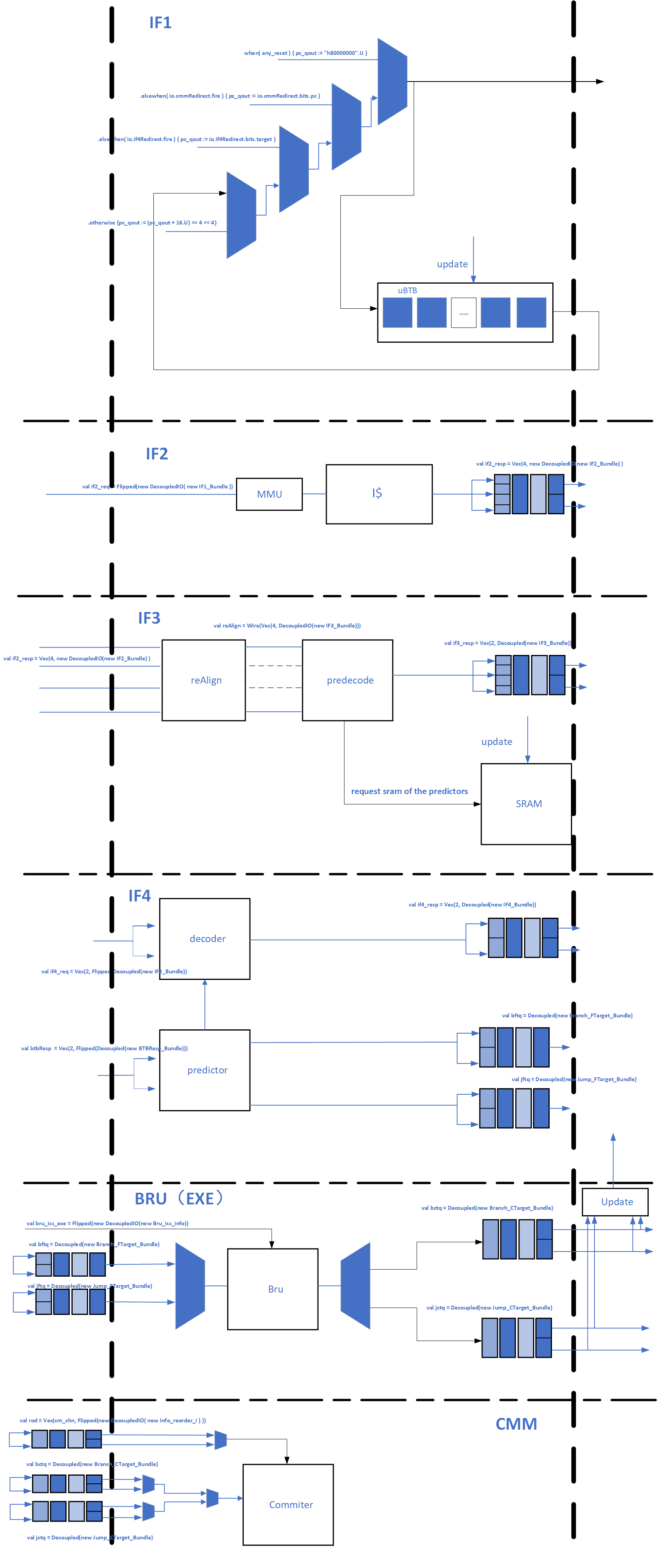

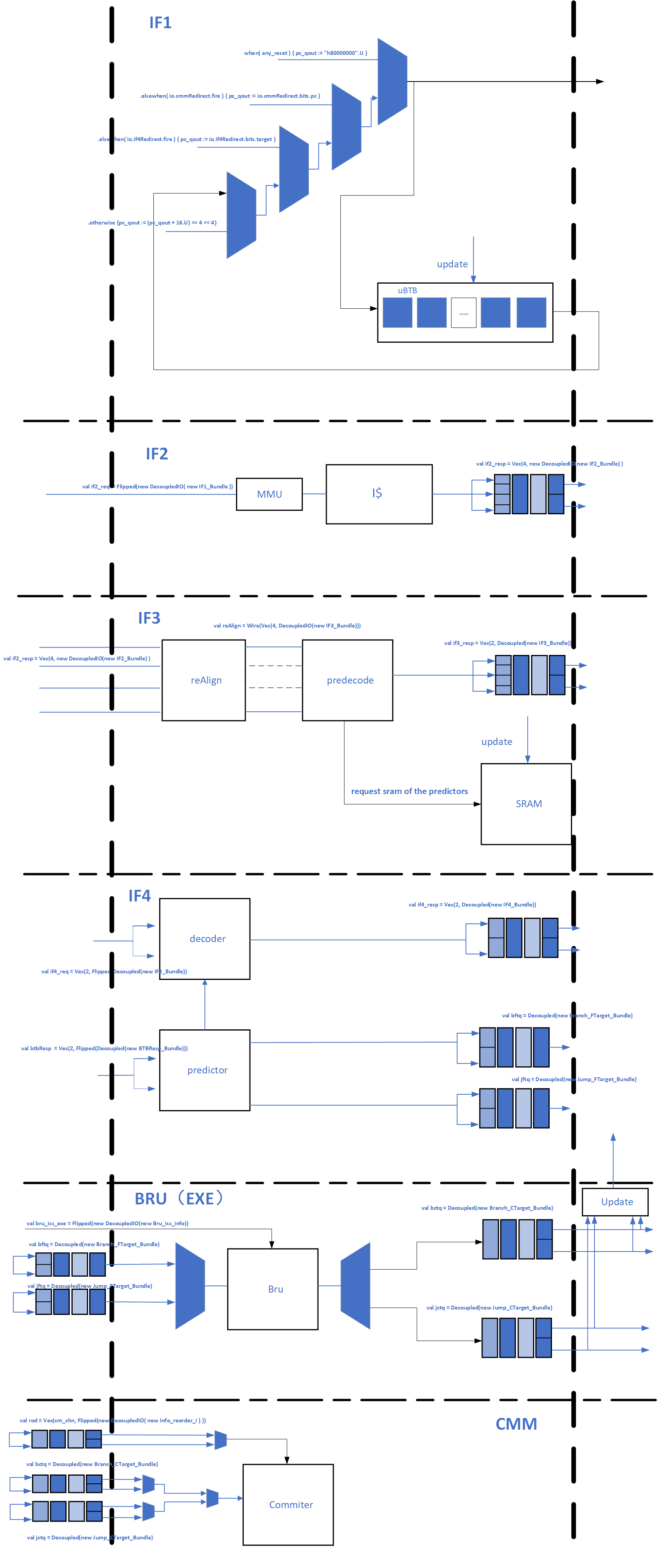

FrontEnd

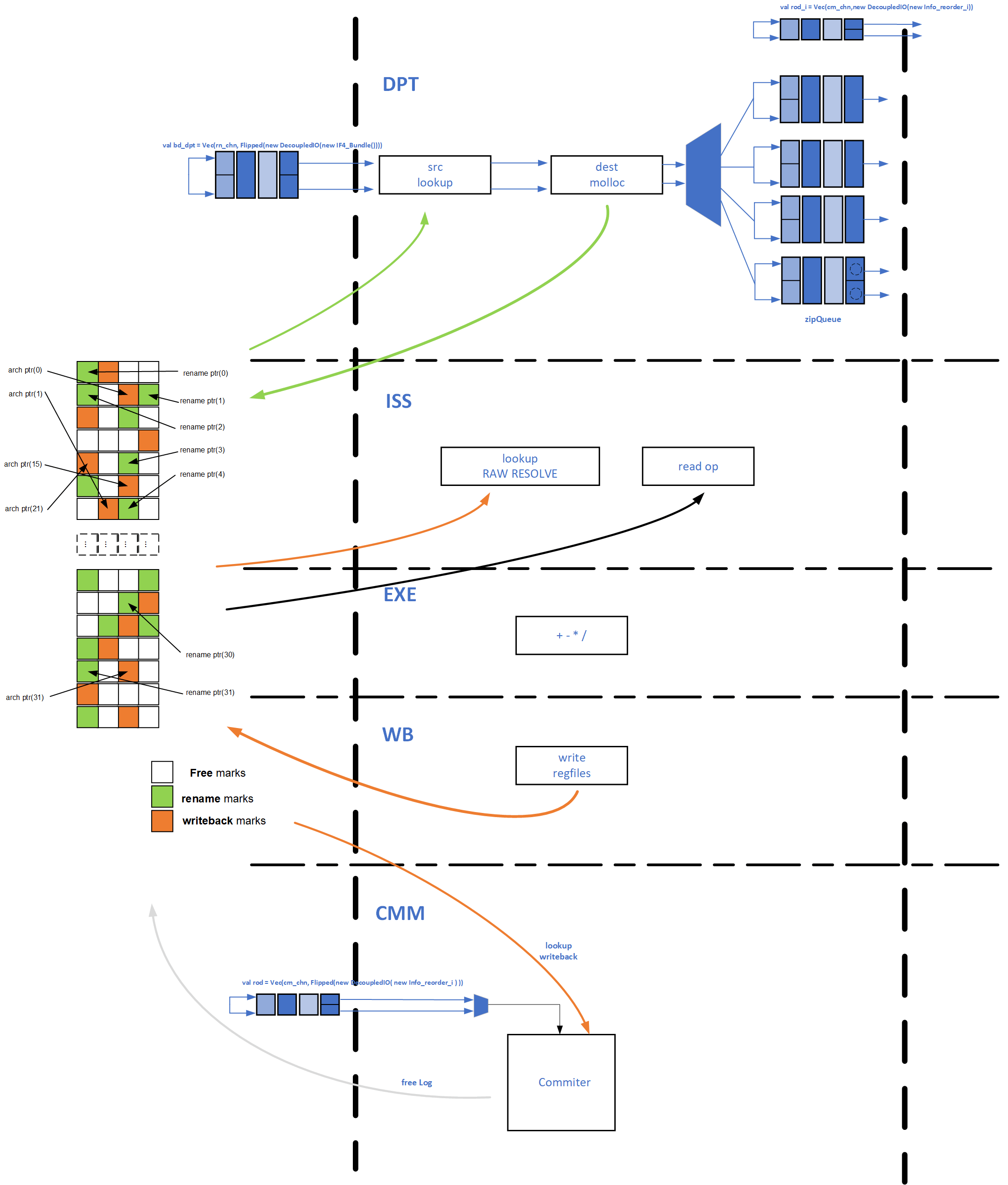

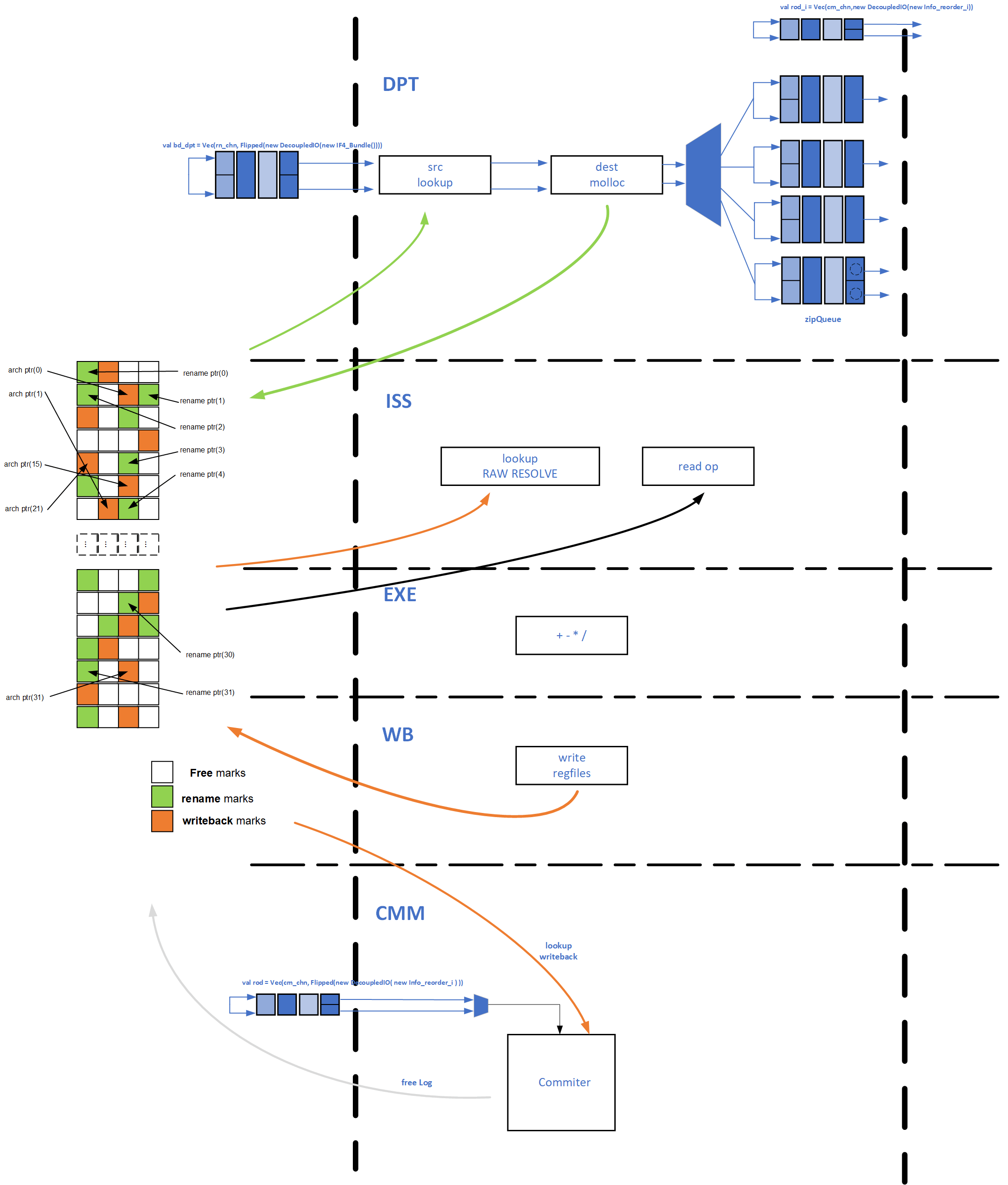

BackEnd