Rsyocto

🤖 SoCFPGA: Open-Source Embedded Linux Distribution with a highly flexible build system, developed for Intel (ALTERA) SoC-FPGAs (Cyclone V & Arria 10)

Install / Use

/learn @robseb/RsyoctoREADME

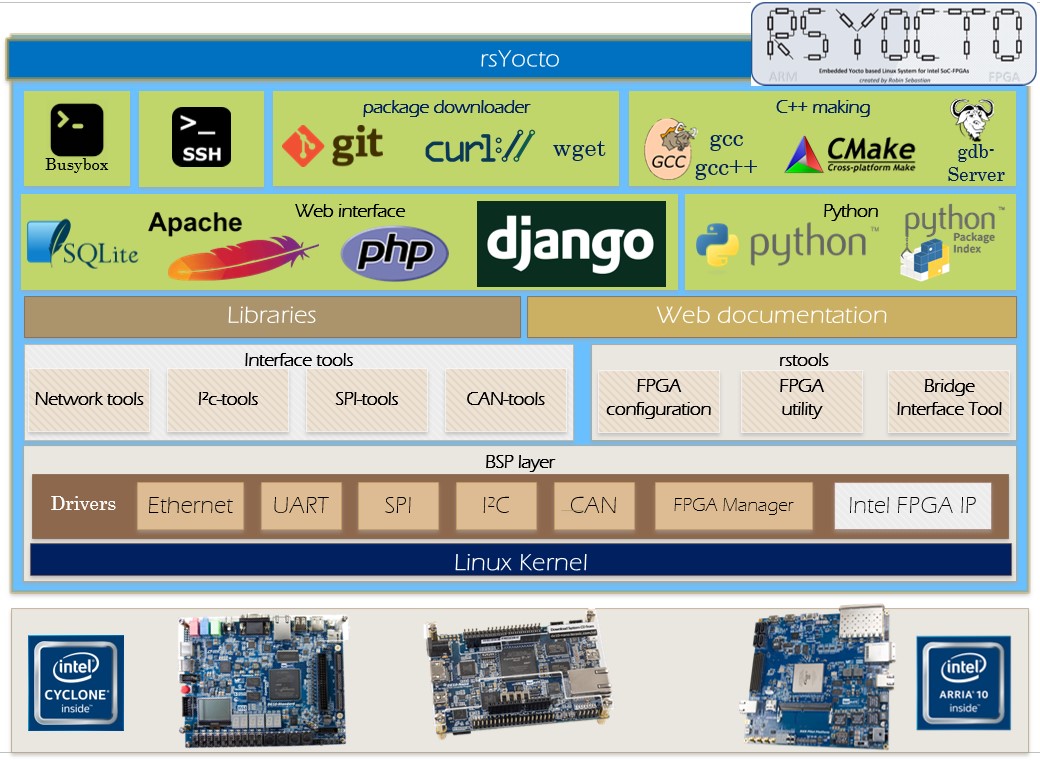

rsyocto is an open source Embedded Linux Distribution designed with the Yocto Project and with a custom build flow to be optimized for Intel SoC-FPGAs (Intel Cyclone V and Intel Arria 10 SX SoC-FPGA with an ARM Cortex-A9) to achieve the best customization for the strong requirements of modern embedded SoC-FPGA applications.

<p align="center"> <img src="https://img.shields.io/static/v1?label=Status&message=active&color=orange"> <a href="https://github.com/robseb/rsyocto/releases"> <img alt="GitHub release (latest by date)" src="https://img.shields.io/github/v/release/robseb/rsyocto"> <img alt="GitHub Releases" src="https://img.shields.io/github/downloads/robseb/rsyocto/latest/total"> <img alt="GitHub Releases" src="https://img.shields.io/github/downloads/robseb/rsyocto/total"> </a> <img src="https://img.shields.io/static/v1?label=Supported+SocFPGA&message=Intel+Arria10,+Cyclone+V&color=blue"> <a href="https://github.com/robseb/rsyocto/issues"> <img alt="GitHub issues" src="https://img.shields.io/github/issues/robseb/rsyocto"> </a> <img src="https://img.shields.io/badge/License-MIT%20-yellow.svg" alt="license"> </p>rsyocto implements a modern Linux Kernel (linux-socfpga 5.11) and brings a set of today fundamentally needed components to Intel SoC-FPGAs to help to simplify the complex process of development for FPGA-, Industrial 4.0-, Internet of things- (IoT), automotive- and deep learning (AI) accelerator- applications.

To realize that Python3 with the Python Package manager pip (PyPI) and the Apache Webserver with PHP are already included. Thereby it is really easy to install Python applications from the Raspberry Pi on a powerful Intel SoC-FPGA. rsyocto is for its best optimization complete console based, but the Apache Webserver can bring any modern GUI to Computers, Smartphones or Tablets, by hosting for example a monitor web interface. For that the Python Web framework Django 3.0 is pre-installed.

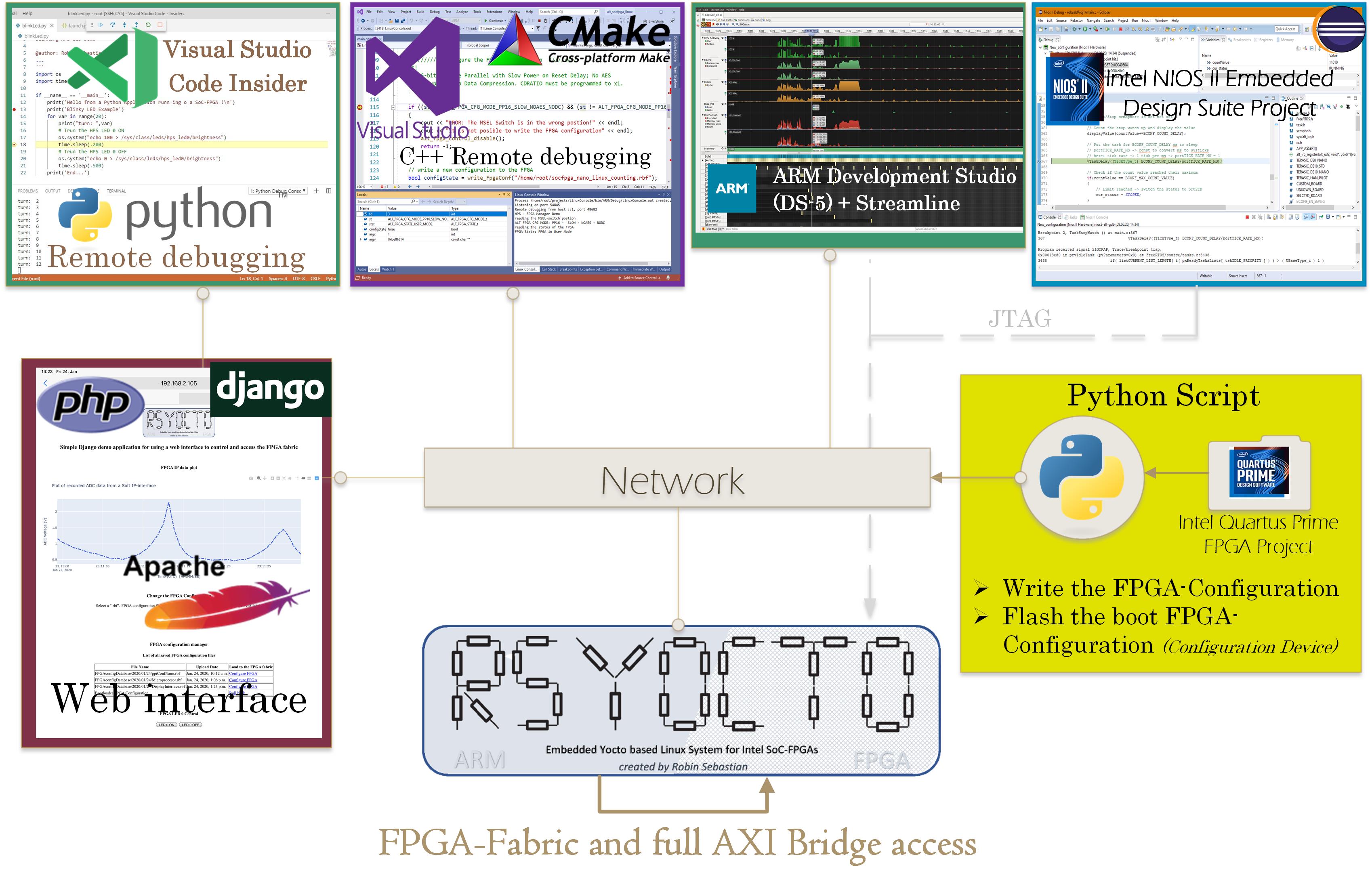

During development, a major concern was placed on the integration of powerful and simple to install development IDEs that do not require a JTAG-connection or any cross-building environment. All kinds of rsyocto applications and parts can be build, deployed and even debugged over the network (fully routable over the Internet). With the implementation of Microsoft Visual Studio and Visual Studio Code a simple installment and quick jump start in the development process is possible, because all required compilers run directly on rsyocto. The custom developed build system goes even a step further.

rsyocto was designed with an automatically Python based build system. That generates a highly optimized customized rsyocto-image with the installment of users private applications, boot configurations, scripts, FPGA-Configuration files, that will be configured on the FPGA Fabric before the Linux boots and a lot more with only an Intel Quartus Prime FPGA project. This feature enables users, without the requirement of deep Linux knowledge, to design own rsyocto flavors with it own FPGA projects for complex Intel SoC-FPGAs. The build system generates the 3-stage bootloader, finds the right Embedded Linux Distribution files, configures the partitions of the final image in the right way, configures theOpenSSH Server and automates a lot more with only an single shell command.

For FPGA developers, a Python script has been developed that allows the FPGA-Configuration to be written over the network (SSH/SFTP) by simply running it in an Intel Quartus Prime FPGA project folder. The script can compile the FPGA project and change the FPGA-Configuration of the bootloader (u-boot) to start the FPGA-Configuration after a restart. This has the same effect as a classic FPGA-Configuration device.

rsyocto is with the implementation of drivers for all Hard-IP Interfaces (e.g. I²C-, CAN-BUS,…), all Interfaces between hard processor system (HPS) and the FPGA Fabric and simple Linux test commands (e.g. i2c-tools or can-utils) ready for the development of industrial connected solutions. For instance, with a single command rsyocto is capable to load a new FPGA-Configuration (FPGA Manager) or to read and write the ARM AXI-Bridge Interface to the FPGA Fabric. The Linux test commands allow in a simple fashion to communicate with the FPGA Fabric via all available interfaces, such as Lightweight HPS-to-FPGA- (lwhps2fpga) , HPS-to-FPGA-Bridge (hps2fpga) , shared-memory (hps2sdram) or general purpose signals (gpi and gpo). Python- and C++- demo applications show a powerful way with a high throughput to interact with FPGA Soft-IP.

The final rsyocto-Image can be installed on a SD-Card with any commonly used Boot-Image creating tools. Versions are available for the Terasic DE10 Standard- (Intel Cyclone V SoC-FPGA), Terasic DE10 Nano- (Intel Cyclone V SoC-FPGA), Terasic Han Pilot (Intel Arria 10 SX SoC-FPGA) and Terasic DE0-Nano SoC (Intel Cyclone V SoC-FPGA).

On the Terasic DE10 Nano board the Arduino Uno header can be used to connect external devices to a Hard-IP Bus, because the HPS interfaces with the pre-installed configuration are routed to FPGA I/O-Pins. An example shows how to use rsyocto, the FPGA-to-HPS-Bridge to access Hard-IP of the HPS with a NIOS II Soft-Core Processor running FreeRTOS. NIOS II Eclipse platforms can also be generated automatically.

<br>I noticed that right now only desktop Linux systems, like Ubuntu, are available for free. In my opinion they are not designed for embedded SoC-FPGAs and therefore, they cannot be considered for long-term embedded systems.

That was for me the starting point to try to develop my own fully optimized Linux distribution. Shortly after, I announced that the Intel development tools and documentations for HPS development are not nearly as good as those for the FPGA part. At the beginning it was really complicated to get anything running. After a hard time, I'm able to present this first working project. To get there, I had to develop my own approach which I think is the best for embedded use-cases by designing my own build flow with my own Python scripts.

I think nearly everybody will have the same problems I had during the development. For that reason, I try to give everybody a solution for their rapid prototyping. Within this repository I have also integrated a step by step guide to show my solution with the openEmbedded Yocto project and the Intel SoC EDS.

With my first versions I got only positive feedback from the community.I will continue my work and upload newer versions. I invite everybody to submit issues, comments and ideas and to support me in other ways...

<br>System Overview of rsyocto

Build, debug and deploy your applications over the network

Ready for powerful remote development IDEs and fitted with a Web server to host modern web applications

<br>

<br>

Ready for powerful remote development IDEs and fitted with a Web server to host modern web applications

<br>

<br>

Key Advantages

-

Embedded Linux specially developed for Intel SoC-FPGAs

- Linux Kernel 5.11 (Source)

-

Full usage of the Dual-Core ARM (ARMv7-A) Cortex-A9 with

- The ARM (SIMD) NEON-Engine

- The Vector Floating Point Unit (VFP)

- The ARM Thumb-2 Instruction Set

- The ARM PL390 Generic Interrupt Controller (GIC)

- The ARM TrustZone for ARMv7-A and Arteris FlexNoC Network-on-Chip Interconnect for the Intel Arria 10 SX

- The ARM CoreSight Debug and Trace Engine with ARM Development Studio (DS-5) support

- The external memory interface controller (EMIF) (SDRAM DDR3/DDR4 controller) of the Intel Arria 10 SX with Early I/O enabled

-

For the best performance completely custom optimized

-

Console based (GUI less) with

Busybox -

Watchdog timer is enabled

-

FPGA Fabric configuration during the boot (u-boot script) and with a single Linux command

-

All Bridge Interfaces between the HPS and FPGA are tested, enabled and ready for use!

-

Tools to interact with the FPGA Fabric via the ARM AXI HPS-to-FPGA bridges

-

Access the FPGA Fabric with Shell scripts, C++-, Python-Applications or PHP or Django web applications

-

HPS Hard IP components (I²C-,SPI-, CAN-BUS or UART) are routed to FPGA I/O

- Ready for connecting different devices

- e.g. Arduino Uno shields

- Ready for connecting different devices

-

Accelerometer and ADC can be accessed via Python or C++ (Demos available) (only for the Cyclone V boards)

-

socketCANpre-installed and pre-configured (examples available!) (Only for Cyclone V SoC-FPGAs) -

Console based Bus test tools (e.g.

can-utils) -

USB Host support with test tools (e.g.

lsusb) -

Console memory dump tools (e.g.

devmem2) -

Full

Linux Network stackwith dynamic and static iPv4 is supported -

OpenSSH-Serverstarts automatically during boot and is configured for user authentications -

UTC Time is synced during bootup with

htpdateand a HTTP Time server -

A virtual software random number generator (RNG) is used (This SoC-FPGAs have no build in TRNG.)

-

resolvconfthe Linux DNS network tool is pre-installed -

Pre-installed development tools and DevOps

gcccompiler 9.3.0glibcandglib-2.0(The GNU C Library)cmake3.16.5Python 3.8Python3-devand `Pytho

Related Skills

node-connect

334.5kDiagnose OpenClaw node connection and pairing failures for Android, iOS, and macOS companion apps

frontend-design

82.2kCreate distinctive, production-grade frontend interfaces with high design quality. Use this skill when the user asks to build web components, pages, or applications. Generates creative, polished code that avoids generic AI aesthetics.

openai-whisper-api

334.5kTranscribe audio via OpenAI Audio Transcriptions API (Whisper).

commit-push-pr

82.2kCommit, push, and open a PR